# DESIGN AND GENERATION OF EFFICIENT HARDWARE ACCELERATORS FOR SPARSE AND DENSE TENSOR COMPUTATIONS

A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by Nitish Kumar Srivastava

May 2020

© 2020 Nitish Kumar Srivastava ALL RIGHTS RESERVED

## DESIGN AND GENERATION OF EFFICIENT HARDWARE ACCELERATORS FOR SPARSE AND DENSE TENSOR COMPUTATIONS

Nitish Kumar Srivastava, Ph.D. Cornell University 2020

Tensor algebra lives at the heart of big data applications. Where classical machine learning techniques such as embedding generation in recommender systems, dimensionality reduction and latent Dirichlet allocation make use of multi-dimensional tensor factorizations, deep learning techniques such as convolutional neural networks, recurrent neural networks and graph learning use tensor computations primarily in the form of matrix-matrix and matrix-vector multiplications. The tensor computations often used in many of these fields operate on sparse data where most of the elements are zeros. Traditionally, tensor computations have been performed on CPUs and GPUs, both of which have low energy-efficiency as they allocate excessive hardware resources to flexibly support various workloads. However, with the end of Moore's law and Dennard scaling, one can no longer expect more and faster transistors for the same dollar and power budget. This has led to an ever-growing need for energy-efficient and high-performance hardware that has resulted in a recent surge of interest in application-specific, domain-specific and behavior-specific accelerators, which sacrifice generality for higher performance and energy efficiency.

In this dissertation, I explore hardware specialization for tensor computations by building programmable accelerators. A central theme in my dissertation is determining common spatial optimizations, computation and memory access patterns, and building efficient storage formats and hardware for tensor computations. First, I present T2S-Tensor, a language and compilation framework for productively generating high-performance systolic arrays for dense tensor computations. Then I present a versatile accelerator, Tensaurus, that can accelerate both dense and mixed sparsedense tensor computations. Here, I also introduce a new sparse storage format that allows accessing sparse data in a vectorized and streaming fashion and thus achieves high memory bandwidth utilization for sparse tensor kernels. Finally, I present a novel sparse-sparse matrix multiplication accelerator, MatRaptor, designed using a row-wise product approach. I also show how these different hardware specialization techniques outperform CPUs, GPUs and state-of-the-art accelerators in both energy efficiency and performance.

#### **BIOGRAPHICAL SKETCH**

Nitish Srivastava was born to Kanchan Srivastava and Kamal Srivastava in a small town Sitapur, Uttar Pradesh, India on December 21st, 1992. Nitish attended Sacred Heart Inter College in Sitapur from 1996–2008. During high school, in addition to his academic studies, Nitish was also interested in sketching and drawing, and has won several district-level drawing competitions with his sister. Nitish went on to pursue mathematics and science in the 11th and 12th grade (junior and senior high school) at Green Field Academy in Hargaon, from 2008–2010.

Determined to obtain an undergraduate degree in Electrical Engineering, Nitish enrolled at the Indian Institute of Technology, Kanpur, India. Nitish took fundamental courses in electrical engineering, physics and mathematics such as micro-electronics, digital VLSI, semiconductor physics, power systems, communication systems, signal processing, classical mechanics, electrodynamics, linear algebra, probability theory, differential equations and multi-variable calculus. Nitish also served as academic mentor, where he helped freshman undergraduates in understanding the key concepts in electrodynamics. Nitish was also secretary for the electronics club at IIT Kanpur, where he helped organize various intra and inter collegiate technical festivals such as Techkriti, Takneek and Electromania. Nitish completed his undergraduate degree in 2014 with the highest GPA in the graduating batch, consisting of all the engineering and science departments at IIT Kanpur, and was awarded with president's gold medal, proficiency medal and Prateek Mishra memorial gold medal.

After undegraduate, Nitish decided to pursue a Ph.D. degree in computer architecture and was offered a graduate fellowship at Cornell University in 2014. At Cornell University, Nitish began his graduate studies under the tutelage of Prof. Rajit Manohar and Prof. David Albonesi. By working with Prof. Rajit's group, he gained invaluable experience in topics such as asynchronous VLSI and circuit design. Soon after Prof. Rajit Manohar moved to Yale University, Nitish continued his Ph.D. at Cornell under the guidance of Prof. Zhiru Zhang and Prof. David Albonesi in topics related to energy-efficient computer architecture, programmability and design of specialized hardware, spatial compilers, and ASIC design.

This document is dedicated to all my teachers, to all my gurus.

#### ACKNOWLEDGEMENTS

This dissertation would not have been possible without the support, encouragement, and advice from many people. First and foremost, I would like to thank my advisors Zhiru Zhang and David Albonesi who have been true mentors and role models throughout my stay at Cornell. Zhiru's passion for research and his ability to grasp things in various different fields whether it be FPGAs, high-level synthesis, machine learning, programming languages, and computer architecture has always amazed and inspired me. Dave's critical thinking, ability to tease out the novel aspects of any research and passion for computer architecture has always inspired me. I would also like to thank Hongbo Rong, my mentor during my internship at Intel, whose skills in programming languages, compilers and spatial architectures helped me a lot in my Ph.D. He has been a great teacher and at the same time a really good friend to me. His constant support and advice has been really fruitful in my research. I would also like to thank the rest of my committee, Christopher Batten and Rajit Manohar, for helping me refine my research with thoughtful feedbacks. I have truly enjoyed working with Chris on HammerBlade, XLOOPS++ and pointer-chase prefetcher projects. Thanks Chris, for teaching me computer architecture and complex ASIC design. Those two courses motivated me to make energy efficient computing as the main focus of my PhD. Thanks Rajit, for teaching me asynchronous VLSI, which allowed me to think hardware design in a completely different way. Thanks to all the members of Zhang Research Group and Albonesi Research Group. Many thanks to Steve Dai who has been a great friend and collaborator. I really enjoyed working with him on the HLS face detection project. I also collaborated with Mathew Watkins, former Ph.D. student in Albonesi group, while working on the CGRA project. His mentorship and advice has been really valuable to me. Matt has been facing some serious health issues for the past one and a half year. I hope for the best for you Matt and hope you will get well soon. I collaborated with Hanchen Jin on the Tensaurus and Hammerblade projects. It was a lot of fun working with him. I also collaborated with Yuwei Hu, Chenhui Deng and Yichi Zhang on the Hammerblade project which was an amazing experience. I appreciate the friendship of Neeraj Kulkarni, who was always there as a really good friend. We did multiple course projects together and it was always fun working and brainstorming ideas with him. I would like to thank Shreesha Srinath and Skand Hurkat for being great mentors and friends during the times when I was struggling to find new research ideas. Despite, I did not collaborate with the rest of the Zhang and Albonesi Research Group, I really appreciate the friendship and support from Gai Liu, Ritchie Zhao, Ecenur Üstün,

Abhinandan Majumdar, Yuan Zhou, Yi-Hsiang (Sean) Lai, Zhenghong (John) Jiang, Cunxi Yu and Jorden Dotzel. I would also like to thank all the friends at CSL.

This dissertation was supported in part by CRISP, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by DARPA, under NSF Awards #1453378, #1512937, #1909661, NSF/Intel CAPA Award #1723773, and by AFRL and DARPA under agreement number FA8650-18-2-7863.

Finally, I would like to thank my family – my parents, sister, brother-in-law and a cute nephew for standing by my side all this time. This journey would not have been possible without you.

|   | -          | graphical Sketch                                                                                     |

|---|------------|------------------------------------------------------------------------------------------------------|

|   | ication    |                                                                                                      |

|   |            | nowledgements                                                                                        |

|   |            | e of Contents                                                                                        |

|   |            | of Figures                                                                                           |

|   |            | of Tables                                                                                            |

|   | List       | of Abbreviations                                                                                     |

| 1 | Intr       | oduction 1                                                                                           |

|   | 1.1        | The Kernel-Sparsity Spectrum                                                                         |

|   |            | 1.1.1 Challenges in Dense Tensor Acceleration                                                        |

|   |            | 1.1.2 Challenges in Sparse Tensor Acceleration                                                       |

|   | 1.2        | The Present and Future of Tensor Computations                                                        |

|   | 1.3        | Dissertation Overview                                                                                |

|   | 1.4        | Collaboration, Previous Publications, and Funding                                                    |

| 2 | Bac        | kground on Tensor Computations 10                                                                    |

| - | 2.1        | Tensor Notations   10                                                                                |

|   | 2.2        | Tensor Factorizations                                                                                |

|   | 2.2        | 2.2.1       Recommendation Systems       10                                                          |

|   |            | 2.2.1         Recommendation systems         11           2.2.2         Model Compression         11 |

|   | 2.3        | Canonical Polyadic Decomposition                                                                     |

|   | 2.3        | Tucker Decomposition   13                                                                            |

|   | 2.4<br>2.5 | Matricized Tensor Times Khatri-Rao Product (MTTKRP)                                                  |

|   | 2.5        | Tensor Times Matrix Chain (TTMc)                                                                     |

|   | 2.0        |                                                                                                      |

|   | 2.1        | 1                                                                                                    |

|   | 2.0        | 2.7.1 Convolutional Layers as Matrix Multiplication                                                  |

|   | 2.8        | Matrix-Vector Multiplication                                                                         |

| 3 |            | -Tensor: Productively Generating High-Performance Spatial Hardware for Dense                         |

|   | Tens       | sor Computations 20                                                                                  |

|   | 3.1        | Introduction                                                                                         |

|   | 3.2        | T2S-Tensor: Overview of the Programming Model                                                        |

|   | 3.3        | T2S-Tensor: High-Level Illustration of the Optimizations                                             |

|   |            | 3.3.1 Temporal Definition                                                                            |

|   |            | 3.3.2 Evolving the Initial Specification into a High-Performance Spatial Design . 25                 |

|   | 3.4        | T2S-Tensor: Compiler Flow and Optimizations                                                          |

|   |            | 3.4.1 Reactive compilation                                                                           |

|   |            | 3.4.2 Proactive compilation                                                                          |

|   | 3.5        | T2S-Tensor: Evaluation                                                                               |

|   |            | 3.5.1 Overall Performance and Productivity                                                           |

|   |            | 3.5.2 Evaluation on the FPGA                                                                         |

|   |            | 3.5.3 Evaluation on the CGRA                                                                         |

### TABLE OF CONTENTS

|   | 3.6  | Related Work                                                                 | 6 |

|---|------|------------------------------------------------------------------------------|---|

|   | 3.7  | Conclusions                                                                  | 7 |

| 4 | Tone | aurus: A Versatile Accelerator for Mixed Sparse-Dense Tensor Computations 48 | 8 |

| - | 4.1  | Introduction                                                                 | - |

|   | 4.2  | Compute Pattern                                                              | - |

|   | 4.3  | Sparse Format         52           52         52                             | - |

|   | 4.4  | Tensaurus Microarchitecture   54                                             |   |

|   | 4.4  | 4.4.1 Implementation Details of Tensaurus                                    |   |

|   | 4.5  | Tensaurus Experimental Setup                                                 |   |

|   | 4.5  | 4.5.1 Simulation Infrastructure                                              |   |

|   |      |                                                                              |   |

|   |      | 4.5.2       Measurements       62         4.5.3       Baselines       63     |   |

|   |      |                                                                              | - |

|   | 16   |                                                                              |   |

|   | 4.6  |                                                                              |   |

|   |      |                                                                              | - |

|   |      | 4.6.2 Performance Evaluation                                                 |   |

|   | 4 7  | 4.6.3 Energy                                                                 | - |

|   | 4.7  | Related Work                                                                 |   |

|   |      | 4.7.1 Sparse Storage Formats                                                 |   |

|   |      | 4.7.2 Software                                                               | - |

|   | 4.0  | 4.7.3 Hardware                                                               |   |

|   | 4.8  | Conclusions                                                                  | / |

| 5 | Mat  | Raptor: A Sparse-Sparse Matrix Multiplication Accelerator Based on Row-Wise  |   |

| U | Proc |                                                                              | 8 |

|   | 5.1  | Introduction                                                                 |   |

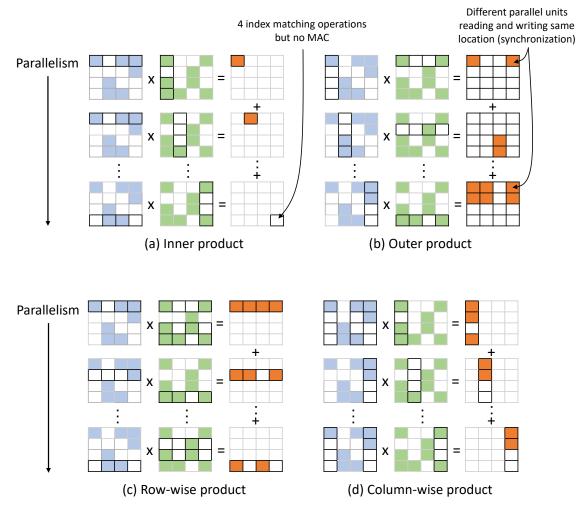

|   | 5.2  | Analysis of SpGEMM Dataflows                                                 | - |

|   | 5.2  | 5.2.1 Inner Product                                                          | - |

|   |      | 5.2.2 Outer Product                                                          |   |

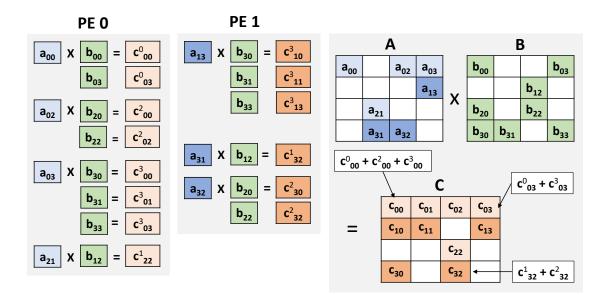

|   |      | 5.2.3 Row-Wise Product                                                       |   |

|   |      | 5.2.4         Column-Wise Product         84                                 |   |

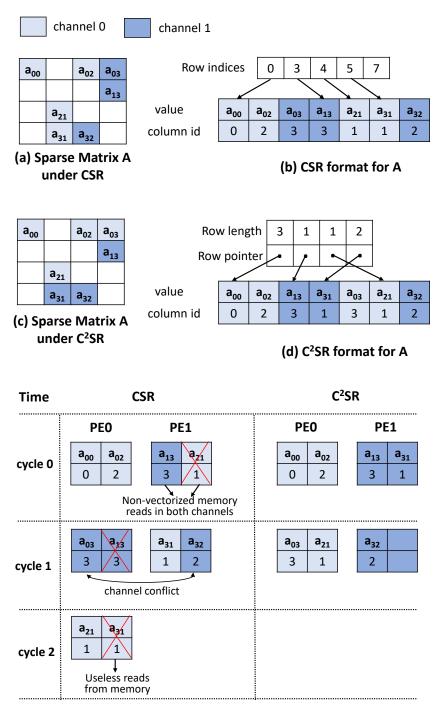

|   | 5.3  | Sparse Matrix Format                                                         |   |

|   | 5.5  | 5.3.1 Limitations of the Traditional CSR Format                              |   |

|   |      | 5.3.2 The Proposed $C^2SR$ Format                                            |   |

|   | 5.4  | MatRaptor Architecture                                                       |   |

|   | 5.4  | 5.4.1 Row-wise Product Implementation                                        |   |

|   |      | 5.4.2 Architectural Details of MatRaptor                                     |   |

|   | 5.5  | 1                                                                            |   |

|   | 5.5  | 1 1                                                                          |   |

|   |      |                                                                              |   |

|   |      | 5.5.2 Measurements                                                           |   |

|   |      | 5.5.3 Baselines                                                              |   |

|   |      | 5.5.4 Technology Node Scaling                                                |   |

|   |      | 5.5.5 Datasets                                                               |   |

|   | 5.6  | Evaluation                                                                   | J |

|     |                  | 5.6.1   | Bandwidth Utilization                                        | 99  |

|-----|------------------|---------|--------------------------------------------------------------|-----|

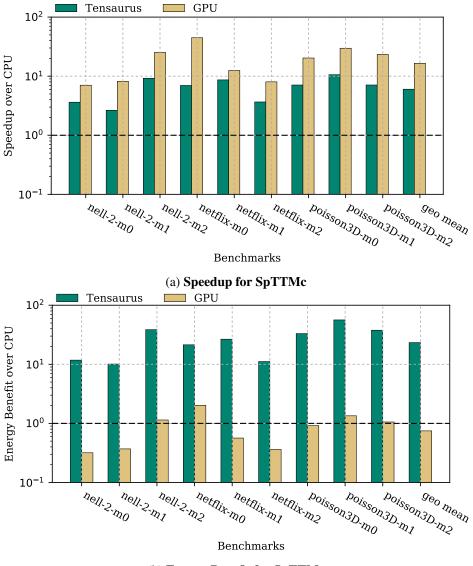

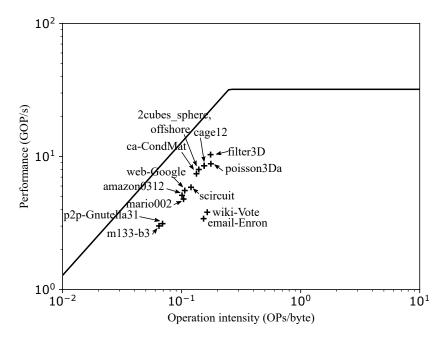

|     |                  | 5.6.2   | Roofline Evaluation                                          | 99  |

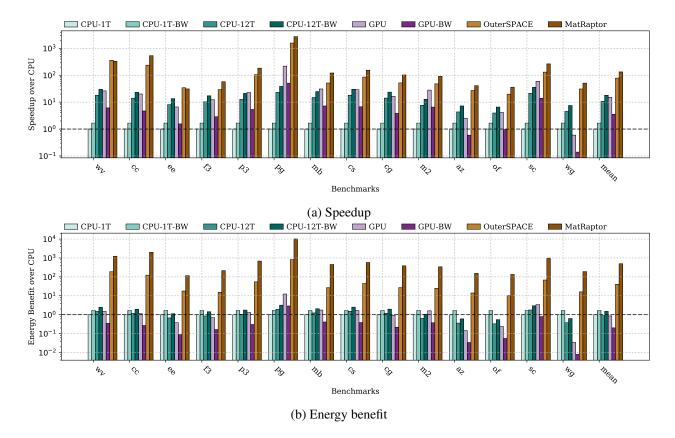

|     |                  | 5.6.3   | Performance Evaluation                                       | 101 |

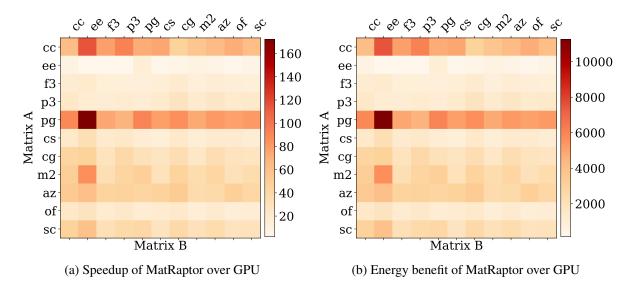

|     |                  | 5.6.4   | Energy                                                       | 102 |

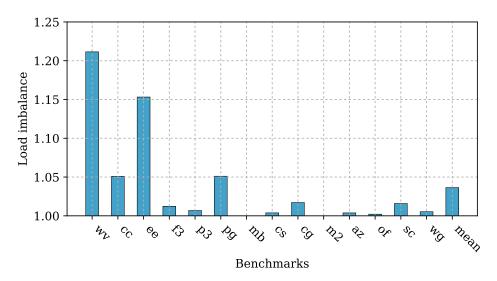

|     |                  | 5.6.5   | Load Imbalance                                               | 103 |

|     | 5.7              | Discus  | sion on Sparse Format                                        | 103 |

|     | 5.8              | Related | 1 Work                                                       | 104 |

|     |                  | 5.8.1   | Sparse Storage Formats                                       | 104 |

|     |                  | 5.8.2   | CPU/GPU Acceleration                                         | 105 |

|     |                  | 5.8.3   | Custom Accelerators                                          | 105 |

|     | 5.9              | Conclu  | ision                                                        | 106 |

| 6   | Con              | clusion |                                                              | 107 |

|     | 6.1              | Dissert | ation Summary and Contributions                              | 107 |

|     | 6.2              | Future  | Work                                                         | 109 |

|     |                  | 6.2.1   | T2S-Tensor for sparse tensors                                | 109 |

|     |                  | 6.2.2   | Processing In Memory for Tensaurus                           | 110 |

|     |                  | 6.2.3   | Accelerating Sparse Convolution Neural Networks on MatRaptor | 110 |

| Bil | Bibliography 111 |         |                                                              |     |

#### LIST OF FIGURES

| 1.1  | Kernel-Sparsity Spectrum of Few Tensor Kernels                              | 3  |

|------|-----------------------------------------------------------------------------|----|

| 2.1  | CP Decomposition of 3-D Tensor                                              | 12 |

| 2.2  | Tucker Decomposition of 3-d Tensor                                          | 14 |

| 2.3  | MTTKRP                                                                      | 15 |

| 2.4  | Convolution Layer as Matrix-Matrix Multiplication                           | 18 |

| 3.1  | An Illustration of T2S-Tensor Approach                                      | 24 |

| 3.2  | Temporal Definition of Matrix-Matrix Multiply, Including Tiling             | 26 |

| 3.3  | Illustrating Some Major Optimizations With GEMM as an Example. For Each     |    |

|      | Optimization, the Corresponding T2S-Tensor Specification is Also Shown      | 27 |

| 3.4  | Loop Removal and Buffer Insertion                                           | 28 |

| 3.5  | T2S-Tensor Code for High-Performance SGEMM Design                           | 30 |

| 3.6  | T2S-Tensor Compiler Flow                                                    | 30 |

| 3.7  | IR for Data Forwarding in C PEs                                             | 32 |

| 3.8  | IR Change After Applying Data Scattering Optimization                       | 33 |

| 3.9  | IR Change for Data Gathering                                                | 34 |

| 3.10 | IR Change for Loop Perfectization                                           | 35 |

| 3.11 | IR Change for Loop Flattening                                               | 36 |

| 3.12 | Loops That Cannot be Infinitized                                            | 37 |

| 3.13 | Complete Design Flow                                                        | 38 |

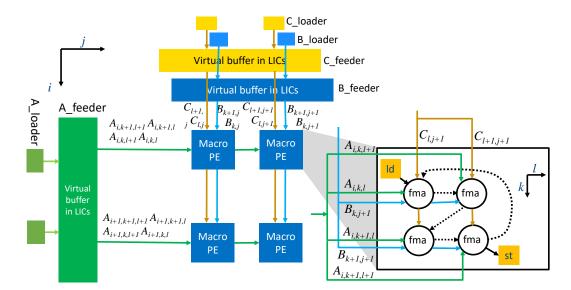

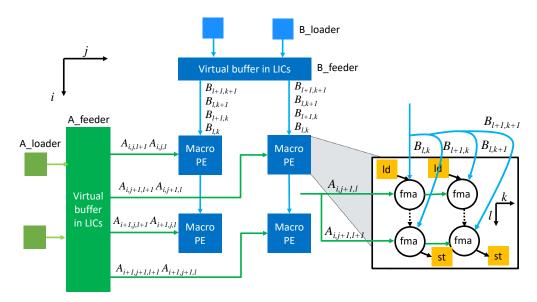

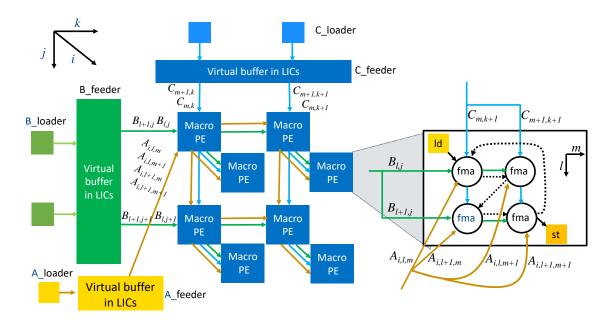

| 3.14 | MTTKRP Design for FPGA                                                      | 40 |

| 3.15 | TTM Design for FPGA                                                         | 40 |

| 3.16 | TTMc Design for FPGA                                                        | 41 |

| 3.17 | GEMM Design for CGRA                                                        | 43 |

| 3.18 | TTM Design for CGRA                                                         | 44 |

| 3.19 | TTM Design for CGRA                                                         | 44 |

| 3.20 | TTMc Design for CGRA                                                        | 45 |

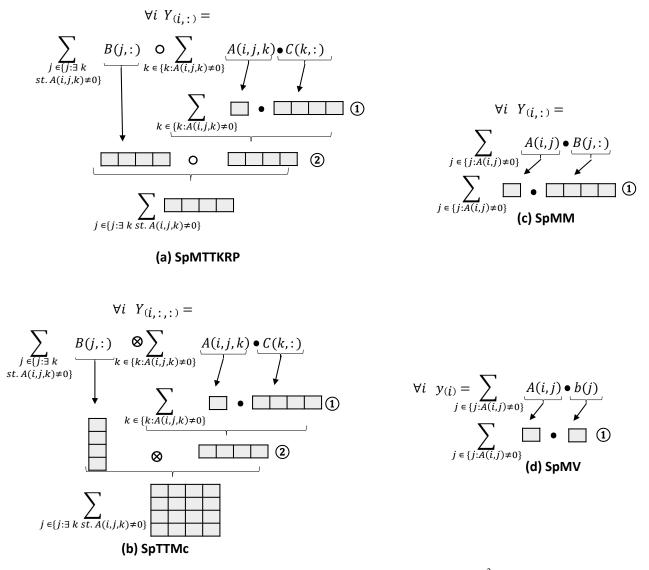

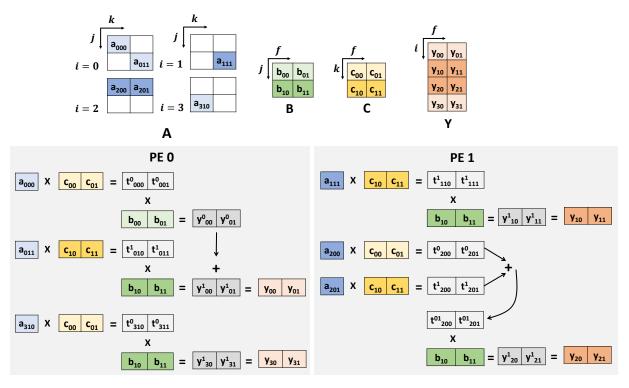

| 4.1  | SpMTTKRP, SpTTMc, SpMM and SpMV Expressed Using the SF <sup>3</sup> Compute |    |

|      | Pattern                                                                     | 50 |

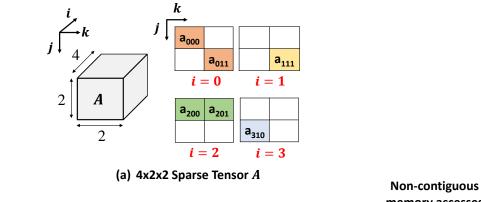

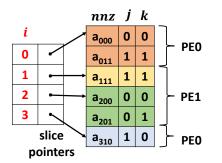

| 4.2  | Storage Formats                                                             | 53 |

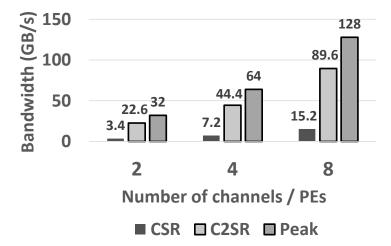

| 4.3  | Memory Bandwidth Comparison                                                 | 54 |

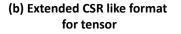

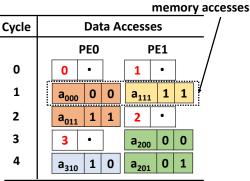

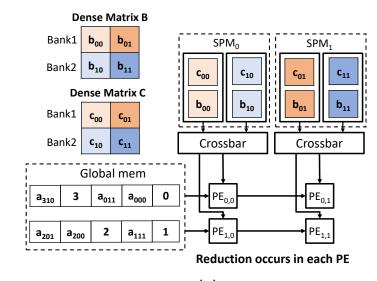

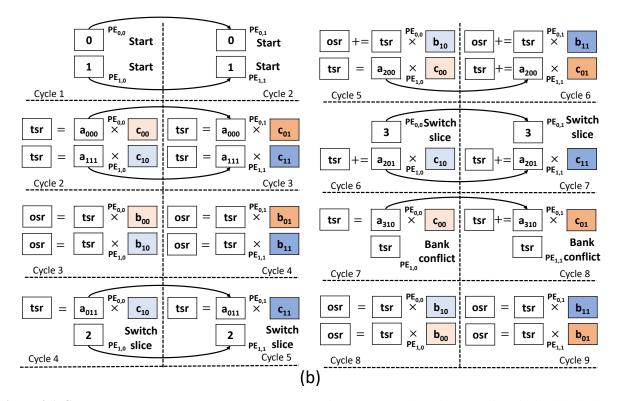

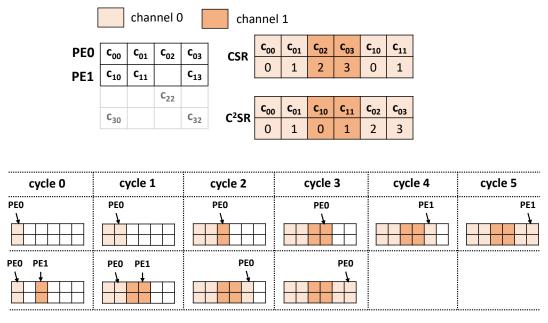

| 4.4  | Cycle by Cycle Execution of SpMTTKRP on Two PEs                             | 56 |

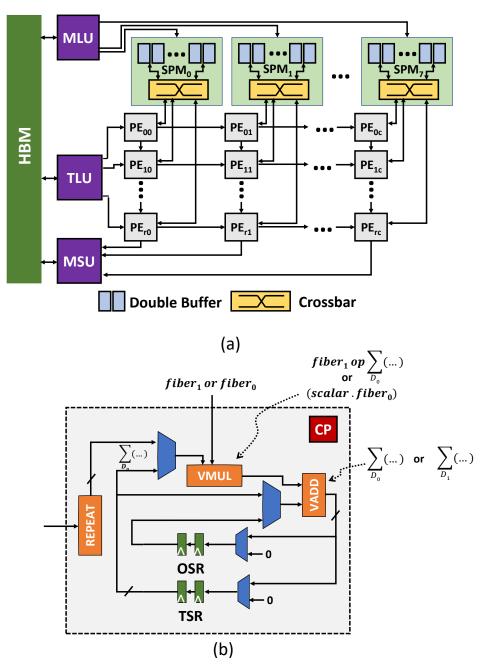

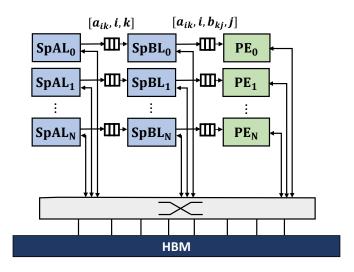

| 4.5  | An Overview of Tensaurus Architecture                                       | 57 |

| 4.6  | SpMTTKRP on Tensaurus                                                       | 60 |

| 4.7  | Roofline for SpMTTKRP                                                       | 66 |

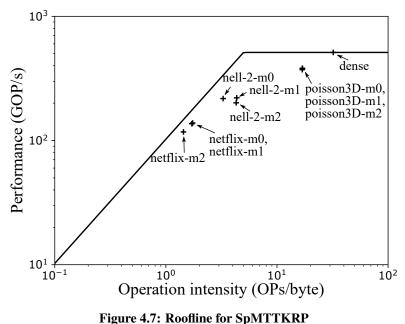

| 4.8  | Roofline for SpTTMc                                                         | 67 |

| 4.9  | Roofline for SpMM                                                           | 67 |

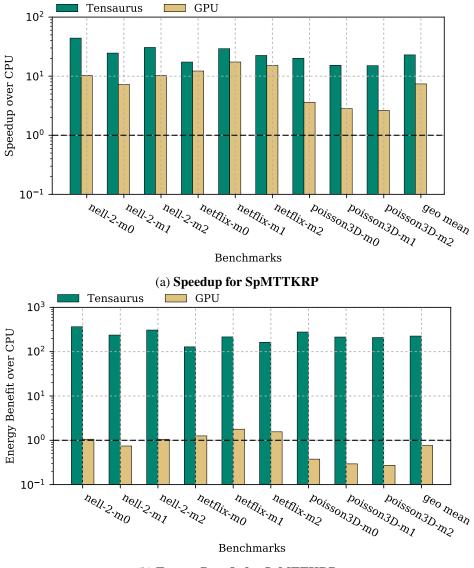

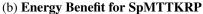

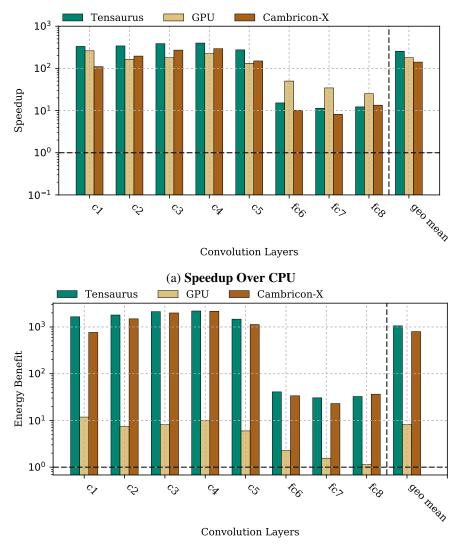

| 4.10 | Speedup and Energy Benefit of Tensaurus for SpMTTKRP                        | 69 |

| 4.11 | Speedup and Energy Benefit of Tensaurus for SpTTMc                          | 70 |

| 4.12 | Speedup and Energy Benefit of Tensaurus for Sparse AlexNet                  | 71 |

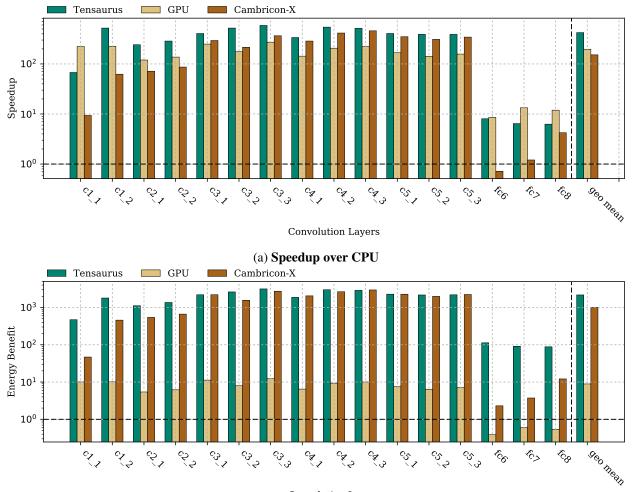

| 4.13 | Speedup and Energy Benefit of Tensaurus for Sparse VGG-16                   | 72 |

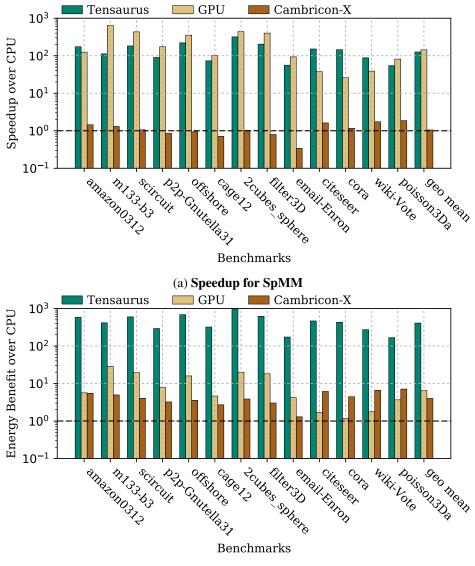

| 4.14 | Speedup and Energy Benefit of Tensaurus for SpMM on SuiteSparse and Graph-      |     |

|------|---------------------------------------------------------------------------------|-----|

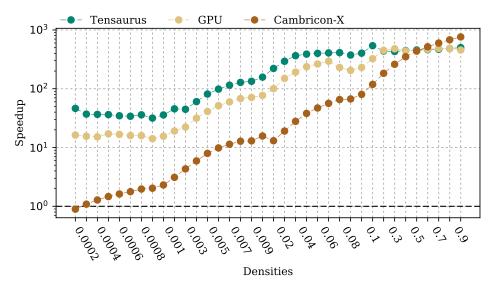

|      | SAGE Matrices                                                                   | 73  |

| 4.15 | Speedup and Energy Benefit of Tensaurus for SpMM on Matrices with Varying       |     |

|      | Density                                                                         | 74  |

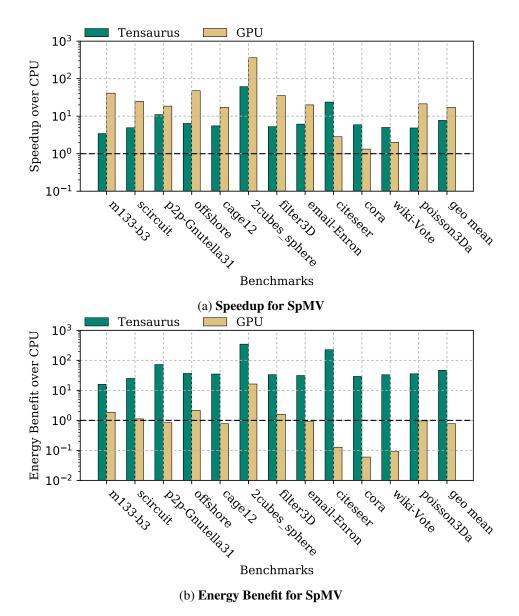

| 4.16 | Speedup and Energy Benefit of Tensaurus for SpMV on GraphSAGE                   | 75  |

| 5.1  | Four Different Ways of Computing SpGEMM Kernel                                  | 80  |

| 5.2  | Parallelization of the Row-Wise Product on two PEs                              | 85  |

| 5.3  | Comparison of Sparse Storage Formats                                            | 87  |

| 5.4  | Comparison of Sparse Storage Formats CSR and $C^2SR$ for Output Matrix          | 88  |

| 5.5  | Illustration of Multiply and Merge Operations Involved in Computing the Results |     |

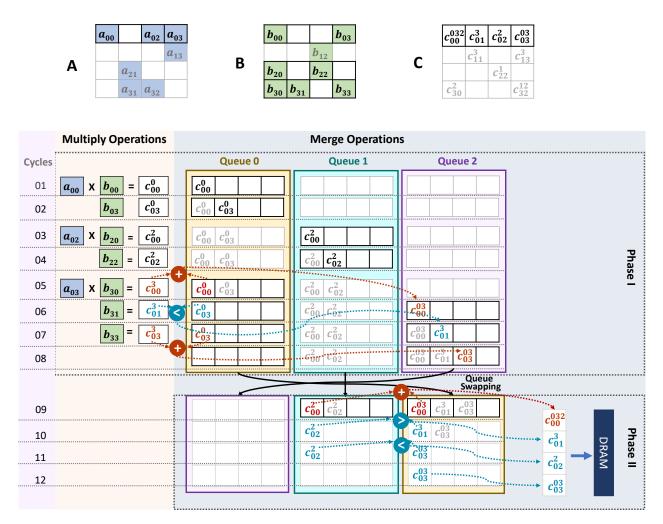

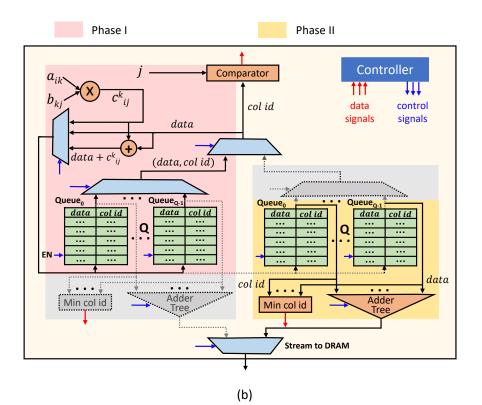

|      | for a Single Row of the Output Matrix in SpGEMM                                 | 90  |

| 5.6  | MatRaptor Architecture                                                          | 93  |

| 5.7  | Achieved Memory Bandwidth with CSR and $C^2SR$                                  | 99  |

| 5.8  | Performance of SpGEMM Under the Roofline of MatRaptor for $A \times A$          | 100 |

| 5.9  | Speedup for A×A over CPU                                                        | 101 |

| 5.10 | Speedup of MatRaptor over GPU-CuSPARSE for A×B                                  | 102 |

| 5.11 | Load Imbalance                                                                  | 103 |

#### LIST OF TABLES

| 3.1 | Definitions of the Tensor Kernels                                             | 37    |

|-----|-------------------------------------------------------------------------------|-------|

| 3.2 | Comparison Between an NDRange OpenCL Baseline, T2S-Tensor and Ninja Im-       |       |

|     | plementations for GEMM on Arria-10 FPGA                                       | 39    |

| 3.3 | Parameters for GEMM, MTTKRP, TTM and TTMc Designs                             | 43    |

| 3.4 | Evaluation Results of MTTKRP, TTM and TTMc in T2S-Tensor on FPGA              | 43    |

| 3.5 | Evaluation Results of T2S-Tensor Designs on the Research CGRA                 | 46    |

| 4.1 | Mapping of DMTTKRP, SpMTTKRP, DTTMc, SpTTMc, GEMM, SpMM, GEMV                 |       |

|     | and SpMV Kernels to the SF <sup>3</sup> Compute Pattern $\ldots$              | 51    |

| 4.2 | Area and Power Breakdown of Tensaurus                                         | 63    |

| 4.3 | Tensors with Their Dimensions, Number of Non-Zeros (nnz), Density and Prob-   |       |

|     | lem Domain                                                                    | 64    |

| 4.4 | Weight Matrices from AlexNet and VGG-16 with Their Dimensions, Number of      |       |

|     | Non-Zeros (nnz) and Density                                                   | 64    |

| 4.5 | Matrices from SuiteSparse with Their Dimensions, Number of Non-Zeros (nnz),   |       |

|     | Density and Problem Domain                                                    | 65    |

| 4.6 | Comparison between the performance of Tensaurus-dense and T2S-Tensor [SRB+198 | l] 71 |

| 5.1 | Area and Power Breakdown of MatRaptor                                         | 97    |

| 5.2 | Matrices from SuiteSparse                                                     | 98    |

#### LIST OF ABBREVIATIONS

| ALS     | alternating least square                   |

|---------|--------------------------------------------|

| CGRA    | coarse-grained reconfigurable architecture |

| CISR    | compressed interleaved sparse row          |

| CNN     | convolution neural network                 |

| CPD     | cannonical polyadic decomposition          |

| CSC     | compressed sparse column                   |

| CSR     | compressed sparse row                      |

| $C^2SR$ | cyclic channel sparse row                  |

| COO     | co-ordinate                                |

| DSL     | domain-specific language                   |

| DSP     | digital signal processing                  |

| FIFO    | first in first out                         |

| FMA     | fused multiply add                         |

| FPGA    | field-programmable gate array              |

| FSM     | finite state machine                       |

| GB/s    | giga-bytes per second                      |

| GEMM    | general matrix-matrix multiplication       |

| GEMV    | general matrix-vector multiplication       |

| GFLOPS  | giga floating point operations per second  |

| GOP/s   | giga operations per second                 |

| HBM     | high bandwidth memory                      |

| HDL     | hardware descriptive language              |

| HOOI    | higher-order orthogonal iterations         |

| HPC     | high-performance computing                 |

| ІоТ     | internet of things                         |

| IR      | intermediate representation                |

| LIC     | latency insensitive channel                |

| LOC     | lines of code                              |

| LUT     | look-up table                              |

| MAC     | multiply-accumulate                        |

| ML      | machine learning                           |

| MTTKRP  | matricized tensor times khatri-rao product |

| PE      | processing engine                          |

| QoR     | quality of result                          |

| RAM     | random access memory                       |

| SCISR   | scalable compressed interleaved sparse row |

| SIMD    | single instruction multiple data           |

| SpGEMM  | sparse matrix-matrix multiplication        |

| SpMM    | sparse matrix dense matrix multiplication  |

| SpMV    | sparse matrix dense vector multiplication  |

| T2S     | temporal to spatial                        |

| TTM     | tensor times matrix                        |

| TTMc    | tensor times matrix chain                  |

## CHAPTER 1 INTRODUCTION

Data-intensive computing significantly impacts the world economy, from warehouse computing to personal mobile devices and Internet of Things (IoT). In this era of data explosion, machine learning (ML) techniques such as social networks, recommendation systems, computational advertising, and image recognition have become pervasive tools in emerging large-scale commercial applications. Tensor algebra lives at the heart of many of these big data applications. For example, multi-dimensional tensor factorizations are extensively deployed in classical ML techniques such as embedding generation in recommender systems, dimensionality reduction, and latent dirichlet allocation [SDLF<sup>+</sup>17, CMDL<sup>+</sup>15, VT02, PFS12]. More recent deep learning techniques such as convolutional neural networks (CNNs), recurrent neural networks (RNNs), and graph learning also make use of tensor computations primarily in the form of matrix-matrix and matrix-vector multiplications [CWV<sup>+</sup>14, VAG17, JYP<sup>+</sup>17]. The tensor computations in these fields often operate on sparse data where most of the elements are zeros. While the underlying computations in all these fields are some basic tensor computations, the sparsity of the tensors can vary significantly among different fields. For example, the graphs in graph learning applications such as Amazon co-purchase network consist of 400K nodes and 3.2M edges forming an adjacency matrix of 400K  $\times$  400K with a density of 0.002%. This is in contrast to sparse deep learning applications such as sparse convolutional neural networks where the weights and activations have a density of 20-40% and the graphs in Internet and social media where the density is in the order of  $10^{-6}$ %. At the same time there are many other ML algorithms that mainly operate on dense tensors.

Traditionally, tensor computations have been performed on CPUs and GPUs [CHW<sup>+</sup>13,ESA<sup>+</sup>06, VSM11], both of which have low energy efficiency as they allocate excessive hardware resources to flexibly support various workloads. For many years, general-purpose processor architectures took advantage of Dennard scaling and Moore's Law. As per Moore's Law [M<sup>+</sup>65], new process technologies reduced feature size of the transistors by a factor of two every 18 months to two years for roughly the same dollar budget. This effectively resulted in exponentially more transistors on a chip for the same cost. Similarly, Dennard Scaling predicted a constant-factor scaling down of feature sizes, voltages, and gate capacitance every 18 months to two years, which led to faster transistors under roughly the same power budget [DGR<sup>+</sup>74]. Because of Moore's Law and Dennard Scaling, applications were transparently becoming faster and more energy efficient with-

out any hardware/software specialization. However today, because of the end of Dennard scaling and an apparent slowing down of Moore's Law, one cannot get more and better transistors. This has caused a recent surge of interest in application- and domain-specific accelerators, which trade generality for higher performance and energy efficiency.

## **1.1 The Kernel-Sparsity Spectrum**

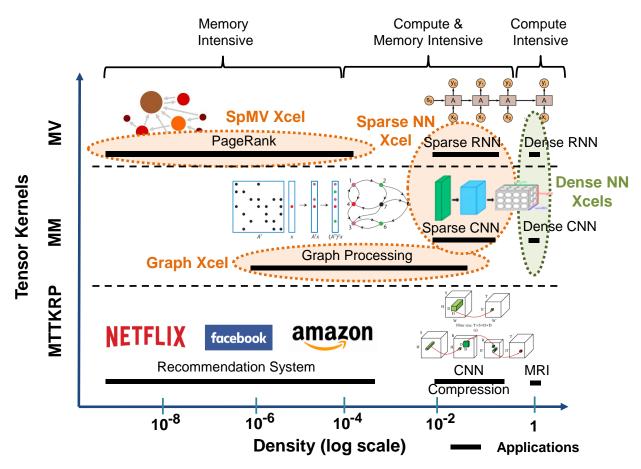

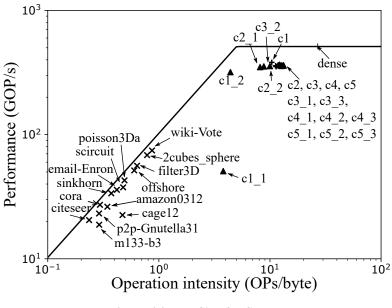

Many real-world tensors are sparse and there are different types of tensor kernels. Fig. 1.1 shows where different application domains lie in the kernel-sparsity space. The x-axis of this spectrum represents density of the tensors in the log domain; The y-axis consists of three representative tensor kernels: matricized tensor times Khatri-Rao product (MTTKRP), matrix-matrix multiplication (MM) and matrix-vector multiplication (MV). As the figure shows, for the same tensor kernel the density of the tensor can vary significantly among the application domains. The existing works on tensor hardware either focus on a single kernel or a single application domain while making assumptions about the sparsity of the tensors [FOS<sup>+</sup>14,HLM<sup>+</sup>16,HKM<sup>+</sup>17,CES16, ZDZ<sup>+</sup>16,JYP<sup>+</sup>17]. The primary reason behind this is that different application domains have different requirements. The applications that operate on very sparse tensors require hardware that is optimized for off-chip and irregular memory accesses, while the applications consisting of dense tensor computations require high on-chip compute resources. I tackle the first challenge by designing sparse tensor formats, which enable efficient off-chip memory accesses for tensors with varying range of sparsity; and the second challenge by designing designing regular systolic arrays with SIMD vectorization to efficiently utilize the on-chip compute resources.

#### 1.1.1 Challenges in Dense Tensor Acceleration

There has been a rich body of research on accelerating dense tensor computations. H.T. Kung and Charles E. Leiserson in their classic 1979 book on Systolic array for VLSI described how most of dense computations lie under the class of systolic algorithms and gave a mathematical foundation of designing systolic arrays for such algorithms [KL79]. Even after four decades, systolic arrays are still considered one of the most efficient ways of performing dense tensor computations. Many state-of-the-art dense tensor accelerators such as Google TPU [JYP<sup>+</sup>17] and NVIDIA Tensor Core [MDCL<sup>+</sup>18] are systolic arrays. The main challenge in the domain of dense tensor

**Figure 1.1: Kernel-Sparsity Spectrum of Few Tensor Kernels** – The solid and black horizontal lines represent the application domains; the orange and green circles represent different application domains for which hardware accelerators have been built.

acceleration, however, is productivity. While the theories behind systolic algorithms and architectures are well understood, building high-performance systolic arrays requires significant efforts in coding and performance tuning. A recent work by Intel shows that it took around 18 months for industry experts to design a high-performance dense matrix-matrix multiplication accelerator using high-level synthesis (HLS) on an FPGA [Ron17a]. The reason behind this is there are numerous hardware optimizations such as tiling, data buffering, and I/O interfacing that need to be handled, apart from expressing the algorithm in a systolic manner, in order to get a high-performance design. These optimizations depend significantly on the amount of available on-chip compute and memory resources such arithmetic and logic units, registers and random-access memories (RAMs), and on the off-chip memory bandwidth. Thus, designing a highly-efficient dense tensor accelerator in a short amount of time still remains a challenge.

#### 1.1.2 Challenges in Sparse Tensor Acceleration

The challenges faced in sparse tensor acceleration are primarily flexibility and efficiency. Unlike dense tensor acceleration, where the datasets are always dense and the hardware for a single tensor kernel such as dense matrix-matrix multiplication can be reused across multiple application domains (e.g., TPU [JYP<sup>+</sup>17]), the same sparse tensor kernel requires different hardware accelerators for different application domains (e.g., SpMV accelerator by Fowers *et al.* [FOS<sup>+</sup>14] for graphs and ESE by Han *et al.* [HKM<sup>+</sup>17] for RNNs, both of which accelerate sparse-dense matrixvector multiplication). This is because the density of the tensors involved in different sparse-tensor application can vary significantly and thus requires different density-dependent hardware and software optimizations such as sparse storage formats, tiling strategies and memory read/write vectorization. This makes the existing sparse tensor accelerators less flexible as they focus on a single tensor kernel or a single application domain while making assumptions about the sparsity of tensors involved in the computation. Thus, designing a hardware accelerator that can flexibly support different sparse tensor kernels with varying ranges of sparsity while being efficient in terms of both energy and performance is a major challenge in sparse tensor acceleration.

### **1.2** The Present and Future of Tensor Computations

The Moore's law and Dennard scaling have slowed down while at the same time data analytics and machine learning are continuously evolving. Below are some observations and predictions on how this might change the future of tensor computations.

**Tensor computations will continue to gain importance.** Today, tensor algebra lives at the heart of data analytics and machine learning. The primary reason behind this is that most of the real-world data whether that be the camera images, video recordings, temperature sensor data or digital circuits come in the form of tensors. Tensors are also a natural way of representing multi-dimensional vector spaces and thus form the basis of many scientific simulations. Both tensor algebra and tensor calculus have been thoroughly studied in the literature and thus tensor based computations are preferred methods in multiple domains. The forms of data that do not have obvious correspondence with tensors such as text documents, speech data, and graphs are often represented as tensors using some embedding techniques [MSC<sup>+</sup>13, MCCD15, GL14]. Today,

with social media and entertainment industry, humans are significantly relying on machines to provide recommendations for movies, clothes, food, and other consumer products. In the near future, machines may be intelligent enough to make decisions for humans, a glimpse of which can be seen with Amazon Echo Dot, OK Google and Siri.

Software for tensor computations will make significant advancements. The first dense matrix algebra library, basic linear algebra subroutines (BLAS) [bla], was developed in 1979, 25 years after the invention of formula translation language (FORTRAN) and 34 years after John von Neumann described modern programmable computers. Over the years, several other dense matrix algebra libraries have been created such as AMD Core Math Library (ACML) [acm], Automatically Tuned Linear Algebra Software (ATLAS) [atl], Intel Math Kernel Library (MKL) [mkl], and OpenBLAS [ope]. In the 1980s, sparse matrix algebra started garnering interest and the first sparse linear algebra library, Sparse BLAS [DHP02], was designed. Later Eigen [GJ<sup>+</sup>10], CSparse [Dav14], PETSc [BAA<sup>+</sup>19], OSKI [VDY05] and other sparse matrix algebra libraries were created. Around the same time researchers realized the power of multi-dimensional tensor algebra and multiple tensor libraries and toolbox such as TeLa [tel] and Cadabra [Pee07] were created. Recently, the growth in deep learning, social media, and human machine interactions resulted in a renewed interest in tensor algebra and many tensor computation libraries and languages such as Tensor Toolbox, GigaTensor [KPHF12], SPLATT [SRSK15], Halide [RKBA<sup>+</sup>13], TensorFlow [ABC<sup>+</sup>16], and TACO [KKC<sup>+</sup>17] were developed. Many of the recent work on tensor languages and libraries such as TensorFlow also not only support CPUs and GPUs but also specialized tensor hardware. As this is just the beginning of the era of machine learning and data analytics, more languages and libraries will be developed to meet the ever-growing needs of tensor computations. Further, with the advancements in tensor hardware these languages and libraries will have specialized backends to target different high-performance tensor hardware.

**Tensor hardware will gain increasing importance.** With the advent of the modern area of deep learning in the last decade, significant advancements have been made both in industry and academia to design energy-efficient and high-performance accelerators for deep learning. Google Tensor Processing Unit (TPU) [JYP<sup>+</sup>17], Microsoft Brainwave [CFO<sup>+</sup>18], and NVIDIA Tensor Core [MDCL<sup>+</sup>18] are a few examples of industry efforts while Eyeriss [CES16], ESE [HKM<sup>+</sup>17], EIE [HLM<sup>+</sup>16], SCNN [PRM<sup>+</sup>17], Cambricon-X [ZDZ<sup>+</sup>16] and DianNao [CCX<sup>+</sup>16] are some

of the efforts made in academia. As deep learning is still in its nascent stage and significant advancements have to be made, tensor hardware will keep on gaining interest. Similar to deep learning, tensor factorizations primarily in the form of recommendation systems have also attracted a great deal of interest in the past few years. This emerging class of applications will require efficient processing and will create a need for more specialized tensor hardware.

## **1.3 Dissertation Overview**

This dissertation presents hardware accelerators and storage formats for accelerating tensor computations. It has two thrusts that tackle two major problems in accelerator design for tensor computations: (1) creating a language and compilation framework for productively designing high-performance accelerators for dense tensor computations, and (2) building versatile accelerators that can accelerate dense and mixed sparse tensor computation. The first thrust provides abstractions, in the form of language primitives, for the computation patterns and spatial optimizations found in dense tensor computations and generating high-performance designs for reconfigurable spatial hardware. This allows programmers to design high-performance hardware accelerators for dense tensor computations in a productive manner. The second thrust extends the domain knowledge gained from (1) to design compute patterns, algorithms, spatial optimizations, and sparse storage formats for sparse tensor computations in order to design flexible and efficient hardware for sparse tensor computations.

Since tensors and tensor computations are the main focus of this dissertation, Chapter 2 presents an extensive background on tensors, tensor factorizations, applications of tensor factorizations, matrix kernels and their applications. The rest of the dissertation is organized as follows. Chapter 3 presents a language and compilation framework for productively generating high-performance systolic arrays for dense tensor computations on spatial architectures. Chapter 4 presents a versatile accelerator that can accelerate both dense and mixed sparse-dense tensor computations. It also proposes a new sparse storage format that allows accessing sparse data in a vectorized and streaming fashion and thus achieves high memory bandwidth utilization for sparse tensor kernels. Chapter 5 presents a novel sparse-sparse matrix multiplication accelerator designed using a row-wise product approach. This chapter also proposes a new sparse storage format that has the same benefits of the sparse storage format in Chapter 4 but also allows using the same format for the output matrix. The key contributions of this dissertation are:

- Proposing a concise yet expressive programming abstraction that decouples spatial mapping from the functional specification of a tensor computation.

- Identifying a set of key spatial optimizations that are essential for creating high-performance spatial hardware for dense tensor computations.

- Proposing a language and compilation framework to productively generate high-performance systolic arrays for dense tensor computations.

- Proposing the first hardware accelerator designed for mixed sparse-dense tensor factorizations. This accelerator is both versatile and adaptable and supports several mixed sparsedense matrix operations for a wide range of sparsity.

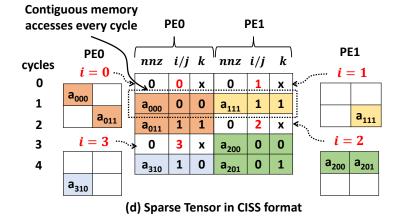

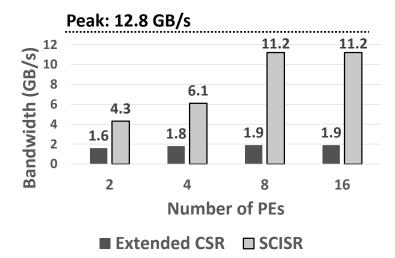

- Proposing a new sparse storage format, compressed interleaved sparse slice (CISS), which allows accessing sparse data in vectorized and streaming fashion and thus helps sparse accelerators achieve high memory bandwidth utilization and performance for sparse tensor kernels.

- Systematically analyzing different dataflows for sparse-sparse matrix multiplication by comparing and contrasting them against data reuse and on-chip memory requirements. It also shows that a row-wise product approach, which has not been explored in the design of sparse-sparse matrix multiplication accelerators, has the potential to outperform the existing approaches.

- Proposing C<sup>2</sup>SR, a new hardware-friendly sparse storage format that allows different parallel processing engines to access the data in a vectorized and streaming manner leading to high utilization of the available memory bandwidth. This format solves the same challenges as in CISS format; however, unlike CISS that can be used only for sparse input matrices but not sparse output matrices, C<sup>2</sup>SR can be used for both.

### **1.4** Collaboration, Previous Publications, and Funding

This dissertation has been made possible by the contributions of many people at Cornell University and Intel Parallel Computing Labs. My Ph.D. advisors, Profs. Zhiru Zhang and David

Albonesi, have been extremely helpful in providing insightful advice, feedback on research ideas, technical writing and presentations. Furthermore, Dr. Hongbo Rong of Intel has been a very valuable mentor and a collaborator for most of the works presented in this dissertation.

The T2S-Tensor project was done as a part of my internship at Intel Parallel Computing Labs under the mentorship of Dr. Rong. This work was later published in International Symposium on Field-Programmable Custom Computing Machines (FCCM) [SRB+19b]. Prithayan Barua, Guanyu Feng and Huanqi Cao had been great collaborators for this project. Additionally, Christohpher Hughes, Paul Petersen, and Pradeep Dubey had been really helpful in providing ideas and feedback for this work. Geoff Lowney, Tim Mattson, Vivek Sarkar and Wenguang Chen gave useful feedback for the paper. Yi-Hsiang Lai, Jie Wang, Weihao Zhao and Size Zheng were the first users of T2S-Tensor who extended this work for general systolic arrays in their work on T2S-Systolic. The Tensaurus project was done a Cornell University and was published in International Symposium on High-Performance Computer Architecture (HPCA) [SJS<sup>+</sup>20]. Hanchen Jin and Shaden Smith were great collaborators for this project, where Hanchen helped in designing the RTL designs for the accelerator and Shaden helped in providing key insights and sparse tensor datasets used for this work. Hongbo Rong had been really helpful in providing ideas and feedback for this work. Alex Coy, Parker Miller, Ayoub Benkhoris and Congyang Li helped in designing high-level synthesis and verilog models for this project. The MatRaptor project was done with the collaboration of Hanchen Jin and Jie Liu and is under submission.

Apart from the three major projects presented in this dissertation, during my Ph.D. I also designed real-time face-detection accelerator [SDMZ17] using high-level synthesis and provided a comprehensive case study to explore the flow from a pure software based implementation to an optimized C++ design suitable for HLS design flow. This accelerator design was later made a part of the Rosetta [ZGD<sup>+</sup>18], which is a realistic benchmark suite for software programmable FPGAs. During my first few years of Ph.D., I also worked on asynchronous circuit design and a proposed novel operation-dependent desynchronization technique [SM18], which desynchronizes the circuit and improves performance beyond the limits of synchronous design.

This research was funded in part by CRISP, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by DARPA, under NSF Awards #1453378, #1512937, #1909661, NSF/Intel CAPA Award #1723773, and by AFRL and DARPA under agreement number FA8650-18-2-7863. The U.S. Government is authorized to reproduce and distribute

reprints for Governmental purposes notwithstanding any copyright notation thereon. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of AFRL and DARPA or the U.S. Government.

## CHAPTER 2 BACKGROUND ON TENSOR COMPUTATIONS

This chapter provides a background on tensor computations. It first introduces tensor notations and then describes the most commonly used tensor computations such as tensor factorizations, matrix-matrix and matrix-vector multiplications.

### 2.1 Tensor Notations

A tensor is a generalization of a matrix to multiple dimensions. A scalar is a tensor of dimension zero, a vector is a tensor of dimension one and a matrix is a tensor of dimension two. We denote tensors with three or more dimensions using capital calligraphic letters (e.g.,  $\mathcal{A}$ ), matrices using boldface capital letters (e.g.,  $\mathbf{A}$ ), vectors using boldface letters (e.g.,  $\mathbf{a}$ ), and scalars using Greek letters (e.g.  $\alpha$ ).

The dimensions of a tensor are also called its modes and colon(:) is used to indicate all the elements of a mode. Thus a 3-dimensional (3-d) tensor is a tensor with 3 modes. Fibers are building blocks of tensors. A fiber is the result of holding all but one index constant. For a 3-d tensor  $\mathcal{A}$ , its fibers are  $\mathcal{A}(:, j, k)$ ,  $\mathcal{A}(i, :, k)$ , and  $\mathcal{A}(i, j, :)$ . Similarly, for a matrix  $\mathbf{A}$  its rows  $\mathbf{A}(i, :)$  and columns  $\mathbf{A}(:, j)$  are its fibers. A slice of a tensor is the resultant matrix by holding all but two indices constant. Slices of a 3-d tensor  $\mathcal{A}$  would be  $\mathcal{A}(i, :, :)$ ,  $\mathcal{A}(:, j, :)$  and  $\mathcal{A}(:, :, k)$ .

### 2.2 Tensor Factorizations

Tensor factorization has two important applications in machine learning: *dimensionality reduction as a learning task*, and *compression of network layers* (e.g., convolutional layers) in deep neural networks.

#### 2.2.1 Recommendation Systems

Matrix and tensor factorization have traditionally been used in recommender systems [SZL<sup>+</sup>05, KB06] to produce factor matrices that represent an *embedding* (e.g., of users and items in user-item pairs) into the reduced latent space. These factor matrices are then used to predict the relevance

"score" of the interaction (e.g., between a user and an item) by simply taking the inner product of their vectors in the latent feature space. With the emergence of larger and more complex data sets, tensor decomposition offers several advantages over matrix- and neural network-based methods. While deep neural networks have produced accurate results in recommendation systems [ZZS<sup>+</sup>18, WFFW17], computer vision [S<sup>+</sup>15, HZRS16], and machine translation [VSP<sup>+</sup>17], they are also *expensive to train*, often requiring large quantities of labeled data, and have *limited interpretability*. In these respects, tensor decomposition can provide a *faster, yet competitive*, method for producing embedding for recommendation systems. Tensor decomposition also allows incorporating new data via coupled [BTK<sup>+</sup>14, DK17] and streaming methods [SHSK18, STF06], without the expensive re-factorization. It also has the advantage that the decomposed factors are more interpretable, as they often map easily to existing concepts [HGS14].

#### 2.2.2 Model Compression

A recent study by Facebook [PNB<sup>+</sup>18] indicates that many important applications in ML: such as recommendations, computer vision, and language models: will soon see increased model complexity, and that a significant fraction of future demand is expected to come from workload corresponding to deep learning *inference*. Therefore, reducing their storage and computation cost will become critical, particularly since many inference workloads will require real-time response, or be computed on the *edge*. In convolutional neural networks in particular, convolution contributes to the bulk of all computation, and compressing this layer (i.e., a 4-D tensor) via tensor decomposition has already been shown to reduce the required data movement and computation, and improve the overall efficiency [CWZZ18, DZB<sup>+</sup>14, LGR<sup>+</sup>14, TXWW15, JVZ14].

The majority of prior studies have focused on matrix factorization. However, real-world data is becoming increasingly higher-order, electronic health records have dimensions that are as high as 85 [LCP<sup>+</sup>17], and keeping data in tensor form retains the multi-way relationship that may otherwise be lost when formulated as a matrix [KB06], and consequently, produces more accurate results [FO17].

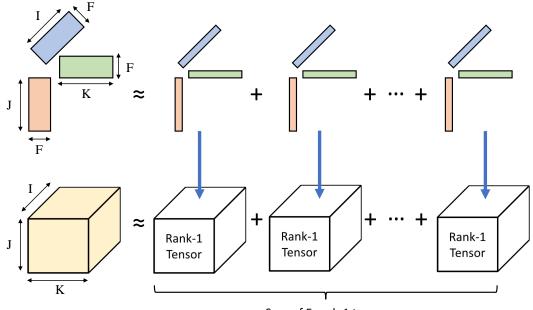

Sum of F rank-1 tensors

Figure 2.1: CP Decomposition of 3-D Tensor

### 2.3 Canonical Polyadic Decomposition

Canonical Polyadic Decomposition (CPD) is one of the most commonly used tensor factorization techniques and is used in fields such as recommender systems [SKB<sup>+</sup>12], signal processing [NS10] and psychometrics [CC70]. CPD is an extension of the Singular Value Decomposition (SVD) to tensors and decomposes a tensor into a summation of F rank-one tensors, where F can either be the rank of the tensor or some smaller integer if a low-rank approximation is desired. A rank-one tensor of order n is the outer product of n vectors. Eq. (2.1) shows how a 3-d tensor is approximated using the outer product of F rank-one tensors.

$$\boldsymbol{\mathcal{X}}(i,j,k) \approx \sum_{f=0}^{F-1} \mathbf{A}(i,f) \mathbf{B}(j,f) \mathbf{C}(k,f)$$

(2.1)

Determining the exact rank of a tensor is NP-hard [Hås90] and we are almost always interested in  $F \ll max(I, J, K)$  for sparse tensors. When computing the rank-F CPD of a 3-d tensor, we wish to find factor matrices  $\mathbf{A} \in \mathbb{R}^{I \times F}$ ,  $\mathbf{B} \in \mathbb{R}^{J \times F}$ , and  $\mathbf{C} \in \mathbb{R}^{K \times F}$  where  $\mathbf{A}$ ,  $\mathbf{B}$ , and  $\mathbf{C}$  are typically dense regardless of the sparsity of  $\mathcal{X}$ .

The method of Alternating Least Squares (ALS) as shown in Algorithm 1 is the most commonly used algorithm for computing the CPD. The computations in Algorithm 1 at line numbers 2, 5 and

#### Algorithm 1 CP-ALS for a mode-3 tensor

**Input**:  $\mathcal{X}$  : A 3rd order tensor F: The rank of approximation **Output**: CP decomposition **A**, **B**, **C**

1: repeat  $\mathbf{A}(i,f) \leftarrow {\textstyle \sum_{j=0}^{J-1} \sum_{k=0}^{K-1} \boldsymbol{\mathcal{X}}(i,j,k) \mathbf{B}(j,f) \mathbf{C}(k,f)}$ 2:  $\mathbf{A} \leftarrow \mathbf{A} (\mathbf{B}^T \mathbf{B} - \mathbf{C}^T \mathbf{C})^{-1}$ 3: Normalize columns of A 4:  $\mathbf{B}(j,f) \leftarrow \sum_{i=0}^{I-1} \sum_{k=0}^{K-1} \boldsymbol{\mathcal{X}}(i,j,k) \mathbf{A}(i,f) \mathbf{C}(k,f)$ 5:  $\mathbf{B} \leftarrow \mathbf{B} (\mathbf{A}^T \mathbf{A} - \mathbf{C}^T \mathbf{C})^{-1}$ 6: Normalize columns of **B** 7:  $\mathbf{C}(k,f) \leftarrow \sum_{i=0}^{I-1} \sum_{j=0}^{J-1} \mathcal{X}(i,j,k) \mathbf{A}(i,f) \mathbf{B}(j,f)$  $\mathbf{C} \leftarrow \mathbf{C} (\mathbf{A}^T \mathbf{A} - \mathbf{B}^T \mathbf{B})^{-1}$ 8: 9: 10: Normalize columns of C 11: **until** no improvement or maximum iterations reached

8 are matricized tensor times Khatri-Rao products (MTTKRP). MTTKRP is thus executed once per mode per iteration of ALS and is often the computational bottleneck of CPD.

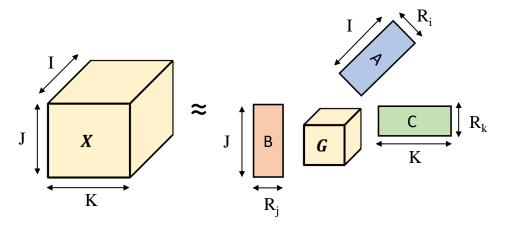

### 2.4 Tucker Decomposition

The objective of Tucker decomposition is to model a tensor  $\mathcal{X}$  with a set of orthonormal matrices and a core tensor. The orthonormal matrices are referred to as factor matrices. Eq. (2.2) shows how a 3-d tensor can be approximated using a core tensor  $\mathcal{G}$  and the factor matrices A, B and C.

$$\boldsymbol{\mathcal{X}}(i,j,k) \approx \sum_{f_k=0}^{F_k-1} \sum_{f_j=0}^{F_j-1} \sum_{f_i=0}^{F_i-1} \boldsymbol{\mathcal{G}}(f_i,f_j,f_k) \mathbf{A}(i,f_i) \mathbf{B}(j,f_j) \mathbf{C}(k,f_k)$$

(2.2)

Several optimization algorithms have been developed to compute Tucker decomposition [DLDMV00a], [DLDMV00b], however, higher-order orthogonal iterations (HOOI) [DLDMV00b] is the most popular algorithm. HOOI is an iterative algorithm that cyclically updates each factor matrix and the core tensor until convergence. Most applications involving tensors perform a low-rank factorization, i.e.,  $max(F_i, F_j, F_k) \ll max(I, J, K)$  for mode-3 tensors.

The computations in Algorithm 2 at line numbers 2, 4 and 6 are tensor times matrix chain (TTMc). TTMc is thus executed once per mode per iteration of HOOI and is often the computational bottleneck of Tucker decomposition.

Figure 2.2: Tucker Decomposition of 3-d Tensor

#### Algorithm 2 HOOI for a mode-3 tensor

**Input**:  $\mathcal{X}$ : A 3rd order tensor  $F_I$ ,  $F_J$ ,  $F_K$ : The ranks of approximation **Output**: Tucker decomposition  $\mathcal{G}$ , A, B, C

1: repeat

- $\mathcal{Y}_0(i, f_j, f_k) \leftarrow \sum_{j=0}^{J-1} \sum_{k=0}^{K-1} \mathcal{X}(i, j, k) \mathbf{B}(j, f_j) \mathbf{C}(k, f_k)$ 2:

- $\mathbf{A} \leftarrow F_I$  leading left singular vectors in mode-0 unfolding of  $\boldsymbol{\mathcal{Y}}_0$ 3:

- $\mathcal{Y}_1(f_i, j, f_k) \leftarrow \sum_{i=0}^{I-1} \sum_{k=0}^{K-1} \mathcal{X}(i, j, k) \mathbf{A}(i, f_i) \mathbf{C}(k, f_k)$ 4:

- $\mathbf{B} \leftarrow F_J \text{ leading left singular vectors in mode-1 unfolding of } \mathcal{Y}_1$  $\mathcal{Y}_2(f_i, f_j, k) \leftarrow \sum_{i=0}^{I-1} \sum_{j=0}^{J-1} \mathcal{X}(i, j, k) \mathbf{A}(i, f_i) \mathbf{B}(j, f_j)$ 5:

- 6:

- $\mathbf{C} \leftarrow F_K$  leading left singular vectors in mode-0 unfolding of  $\mathcal{Y}_2$ 7:

- $\mathcal{G}(f_i, f_j, f_k) \leftarrow \sum_{k=0}^{K-1} \mathcal{Y}_2(f_i, f_j, k) \mathbf{C}(k, f_k)$ 8:

- 9: until no improvement or maximum iterations reached

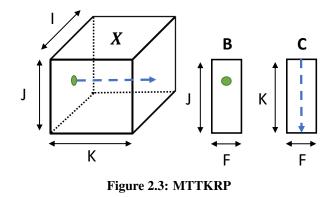

#### 2.5 Matricized Tensor Times Khatri-Rao Product (MTTKRP)

MTTKRP is the key computation kernel in the alternating least square (ALS) method, which is the most popular method for finding the factor matrices in CPD [SDLF<sup>+</sup>17, KB09]. The computation for MTTKRP consists of multiplication of a tensor with N-1 factor matrices, where N is the mode of the tensor, to produce an output matrix. Eq. (2.3) shows the MTTKRP kernel for a 3-d tensor along mode 0 (*i*), where  $\cdot$  denotes multiplication. Since MTTKRP is used for both sparse and dense tensor factorizations [BHR18], I refer to MTTKRP on sparse tensors as SpMTTKRP and on dense tensors as DMTTKRP. The input matrices and the output matrix in both SpMTTKRP and DMTTKRP are dense. Even with very efficient data structures [SRSK15, LSV18], the arithmetic intensity of SpMTTKRP remains low, making this kernel memory bound [CLSS18].

The Hadamard product, denoted by  $\circ$ , is the element-wise multiplication of two matrices with the same dimensions. It is distributive and can be used to factor out the operand matrices in

MTTKRP [SRSK15] as shown in Eq. (2.4). Here the Hadamard product operates on two vectors instead of two matrices. Such factorization reduces the number of multiplications in DMTTKRP from  $2I \cdot J \cdot K \cdot F$  to  $I \cdot J \cdot F \cdot (K+1)$ . Here *I*, *J* and *K* are the sizes of the three dimensions of the tensor and *F* is the desired rank for tensor factorization (normally in the order of 10s to 100s). Eq. (2.4) can be easily generalized to MTTKRP on tensors with more than three dimensions as shown in Eq. (2.5).

$$\mathbf{Y}(i,f) = \sum_{j=0}^{J-1} \sum_{k=0}^{K-1} \mathcal{A}(i,j,k) * \mathbf{B}(j,f) * \mathbf{C}(k,f)$$

(2.3)

$$\mathbf{Y}(i,:) = \sum_{j=0}^{J-1} \mathbf{B}(j,:) \circ \left(\sum_{k=0}^{K-1} \mathcal{A}(i,j,k) * \mathbf{C}(k,:)\right)$$

(2.4)

$$\mathbf{Y}(i_1,:) = \sum_{i_2} \mathbf{M}_2(i_2,:) \circ \dots \circ \sum_{i_n} \mathcal{A}(i_1,\dots,i_n) \cdot \mathbf{M}_n(i_n,:)$$

(2.5)

Similarly, MTTKRP on sparse tensors with and without operand factoring can be represented as Eq. (2.6) and (2.7). The reductions in number of operations in the case of SpMTTKRP with operand factoring are similar to its dense counterpart [SRSK15].

$$\mathbf{Y}(i,f) = \sum_{\substack{j \in \{j \mid \exists k \text{ st.} \\ \mathcal{A}(i,j,k) \neq 0\}}} \sum_{\substack{k \in \{k \mid \\ \mathcal{A}(i,j,k) \neq 0\}}} \mathcal{A}(i,j,k) * \mathbf{B}(j,f) * \mathbf{C}(k,f)$$

(2.6)

$$\mathbf{Y}(i,:) = \sum_{\substack{j \in \{j \mid \exists k \text{ st.} \\ \mathcal{A}(i,j,k) \neq 0\}}} \mathbf{B}(j,:) \circ \left(\sum_{\substack{k \in \{k \mid \\ \mathcal{A}(i,j,k) \neq 0\}}} \mathcal{A}(i,j,k) * \mathbf{C}(k,:)\right)$$

(2.7)

### **2.6** Tensor Times Matrix Chain (TTMc)

TTMc involves a sequence of tensor times matrix operations along each mode, which compresses the tensor. The output of TTMc is another tensor compressed for all but one mode. Eq. (2.8)shows the TTMc kernel for a 3-d tensor along mode 0 (*i*). Similar to MTTKRP, TTMc is used for both dense and sparse tensors [CCJ<sup>+</sup>17, BKK19, CLC18]. Accordingly, I refer to TTMc on sparse tensors as SpTTMc and on dense tensors as DTTMc. For both SpTTMc and DTTMc, the operand matrices and output tensor are dense.

The Kronecker product, denoted by  $\otimes$ , is the generalization of the vector outer product to matrices and tensors. It is also distributive and can be used to factor out the operand matrices in TTMc as shown in Eq. (2.9). Such factorization reduces the number of multiplications in DTTMc from  $2 \cdot I \cdot J \cdot K \cdot F_1 \cdot F_2$  to  $I \cdot J \cdot (K \cdot F_2 + F_1 \cdot F_2)$ . Here  $F_1$  and  $F_2$  are in the order of 10s to 100s. Eq. (2.9) can also be easily generalized to tensors with more than three dimensions as shown in Eq. (2.10).

$$\boldsymbol{\mathcal{Y}}(i,f_1,f_2) = \sum_{j=0}^{J-1} \sum_{k=0}^{K-1} \boldsymbol{\mathcal{A}}(i,j,k) * \mathbf{B}(j,f_1) * \mathbf{C}(k,f_2)$$

(2.8)

$$\boldsymbol{\mathcal{Y}}(i,:,:) = \sum_{j=0}^{J-1} \mathbf{B}(j,:) \otimes \left(\sum_{k=0}^{K-1} \boldsymbol{\mathcal{A}}(i,j,k) * \mathbf{C}(k,:)\right)$$

(2.9)

$$\boldsymbol{\mathcal{Y}}(i_1,:,..,:) = \sum_{i_2} \mathbf{M}_2(i_2,:) \otimes \ldots \otimes \sum_{i_n} \boldsymbol{\mathcal{A}}(i_1,...,i_n) \cdot \mathbf{M}_n(i_n,:)$$

(2.10)

Similarly, TTMc on sparse tensor with and without operand factoring can be represented as Eqs. (2.11) and (2.12) and the reductions in number of operations performed for SpTTMc in the case of operand factoring are similar to the ones for DTTMc [SK17].

$$\boldsymbol{\mathcal{Y}}(i,f_1,f_2) = \sum_{\substack{j \in \{j \mid \exists k \text{ st.} \\ \boldsymbol{\mathcal{A}}(i,j,k) \neq 0\}}} \sum_{\substack{k \in \{k \mid \\ \boldsymbol{\mathcal{A}}(i,j,k) \neq 0\}}} \boldsymbol{\mathcal{A}}(i,j,k) * \mathbf{B}(j,f_1) * \mathbf{C}(k,f_2)$$

(2.11)

$$\boldsymbol{\mathcal{Y}}(i,:,:) = \sum_{\substack{j \in \{j \mid \exists k \text{ st.} \\ \boldsymbol{\mathcal{A}}(i,j,k) \neq 0\}}} \mathbf{B}(j,:) \otimes \left(\sum_{\substack{k \in \{k \mid \\ \boldsymbol{\mathcal{A}}(i,j,k) \neq 0\}}} \boldsymbol{\mathcal{A}}(i,j,k) * \mathbf{C}(k,:)\right)$$

(2.12)

### 2.7 Matrix-Matrix Multiplication

Matrix-matrix multiplication multiplies two matrices **A** and **B** to produce an output matrix **C**. Matrix-matrix multiplication where both **A** and **B** are dense is called general matrix-matrix multiplication (GEMM); the case where **A** is sparse and **B** is dense is called sparse-dense matrix-matrix multiplication (SpMM); and the case where both **A** and **B** are sparse is called generalized sparse matrix-matrix multiplication or sparse-sparse matrix-matrix multiplication (SpGEMM). GEMM and SpMM are building blocks of many algorithms such as graph learning [HYL17, KW16] and CNNs [CWV<sup>+</sup>14], and SpGEMM is a key kernel in algorithms such as graph contraction [GRS08]. In the literature, researchers have used the term SpMM for both sparse-dense and sparse-sparse matrix multiply; however, for clarity, I will use the term SpMM for sparse-dense, and SpGEMM for sparse-sparse matrix-matrix multiply. Eqs. (2.13), (2.14) and (2.15) show the computations for GEMM, SpMM and SpGEMM.

$$\mathbf{Y}(i,f) = \sum_{j=0}^{J-1} \mathbf{A}(i,j) * \mathbf{B}(j,f)$$

(2.13)

$$\mathbf{Y}(i,f) = \sum_{\substack{j \in \{j \mid \\ \mathbf{A}(i,j) \neq 0\}}} \mathbf{A}(i,j) * \mathbf{B}(j,f)$$

(2.14)

$$\mathbf{Y}(i,f) = \sum_{\substack{j \in \{j \mid \\ \mathbf{A}(i,j) \neq 0 \\ \mathbf{B}(j,f) \neq 0 \}}} \mathbf{A}(i,j) * \mathbf{B}(j,f)$$

(2.15)

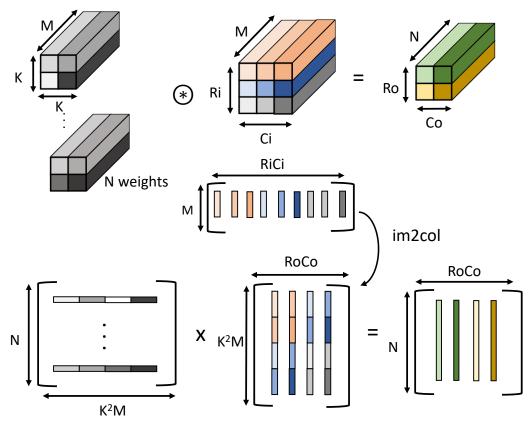

#### 2.7.1 Convolutional Layers as Matrix Multiplication

A CNN is a directed acyclic graph of many computation layers. Each layer of a CNN takes input data, also known as the input feature map, performs some computations, and outputs an output feature map. The computational bottleneck of a CNN are the convolutional (CONV) layers, which perform high dimensional convolution. Eq. (2.16) shows the computation within a single CONV layer.

$$\mathcal{O}[n][r_o][c_o] = \sum_{m,k_y,k_x} \mathcal{I}[m][r_o + k_y][c_o + k_x] * \mathcal{W}[n][m][k_y][k_x]$$

(2.16)

Figure 2.4: Convolution Layer as Matrix-Matrix Multiplication

Here  $\mathcal{O}$  and  $\mathcal{I}$  are 3-dimensional tensors for the output feature and input feature maps, respectively, and  $\mathcal{W}$  is a 4-dimensional tensor for the weights. The computation in CONV layers is easily mapped to matrix-matrix multiplication as shown in Fig. 2.4 by organizing the weights and input feature maps as matrices [CPS06].

### 2.8 Matrix-Vector Multiplication

Matrix-vector multiplication involves multiplication of a matrix with a vector to produce an output vector. Matrix-vector multiplication involving a dense matrix and a dense vector is known as general matrix-vector multiplication (GEMV), and a sparse matrix and a dense vector is known as sparse-dense matrix-vector multiplication (SpMV). GEMV and SpMV are used in applications such as PageRank [BP98], RNNs, minimal spanning tree, single-source shortest path and ML algorithms such as support vector machine [NMM15] and text analytics [MNV<sup>+</sup>17]. Eq. (2.17) and (2.18) show the computations for GEMV and SpMV.

$$\mathbf{y}(i) = \sum_{j=0}^{J-1} \mathbf{A}(i,j) * \mathbf{b}(j)$$

(2.17)

$$\mathbf{y}(i) = \sum_{\substack{j \in \{j \mid \\ \mathbf{A}(i,j) \neq 0\}}} \mathbf{A}(i,j) * \mathbf{b}(j)$$

(2.18)

## CHAPTER 3 T2S-TENSOR: PRODUCTIVELY GENERATING HIGH-PERFORMANCE SPATIAL HARDWARE FOR DENSE TENSOR COMPUTATIONS

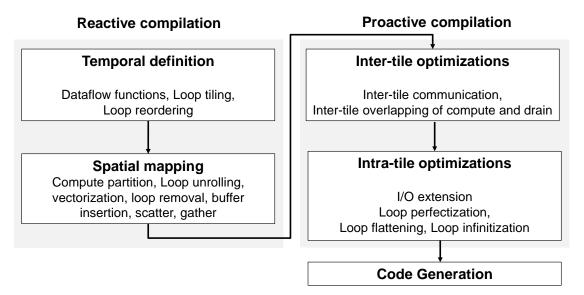

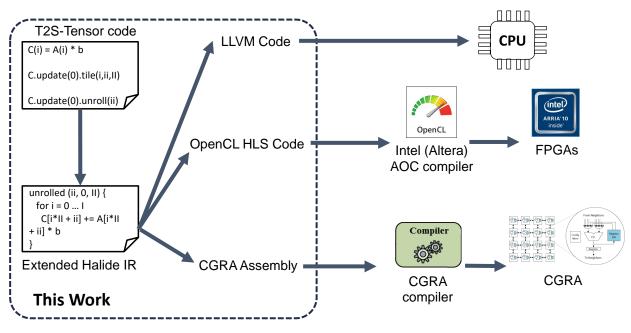

This chapter explores hardware acceleration of dense tensor computations on spatial hardware such as FPGAs and CGRAs. T2S-Tensor provides a language and compilation framework for productively generating high-performance systolic arrays for dense tensor kernels on spatial architectures. T2S-Tensor decouples a functional specification from a spatial mapping, allowing programmers to quickly explore various spatial optimizations for the same function. The actual implementation of these optimizations is left to a compiler. Thus, productivity and performance are achieved at the same time.

### 3.1 Introduction

High-performance computing (HPC) on spatial architectures tends to be limited by very low design productivity — it is not unusual for industry experts to spend several months or even more than a year to deliver one seemingly simple kernel with good quality of results (QoRs). While HPC programming is presumably challenging on any architecture including CPUs/GPUs, it is especially painful on spatial architectures like field-programmable gate arrays (FPGAs) due to their much longer compile time and primitive debugging support [Ron17b]. In addition, FPGA designs often require construction of specialized user-managed on-chip memory hierarchy, which significantly increases the programming complexity. Coarse-grain reconfigurable architectures (CGRAs) have been proposed to address the slow compilation problem, but how to efficiently program CGRAs remains an open question.

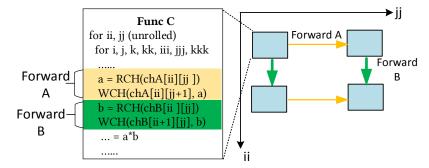

To address these long-standing challenges, I propose a novel programming system consisting of a language and compiler, named T2S(Temporal To Spatial)-Tensor, for productively generating high-performance spatial hardware for dense tensor computations. I observe that *a dense tensor computation suitable for a spatial architecture is usually a dataflow function, and a highperformance spatial design partitions the computation into many sub-computations. These subcomputations are distributed over the spatial architecture, and are connected with channels, i.e. FIFOs. They run in parallel, and are individually optimized by a series of loop and data transfor-* *mations*. Based on this observation, T2S-Tensor enables programmers to describe a tensor computation in a functional notation, followed by a spatial mapping that describes compute partition and loop and data transformation optimizations. A compiler then composes these optimizations and synthesizes them to run on a spatial architecture. Thus, T2S-Tensor allows programmers to succinctly *specify* different optimizations and leave the actual implementation of the optimizations to the compiler.

Well-known dense tensor kernels include, for example, general matrix multiply (GEMM), tensor times matrix (TTM), matricized tensor times khatri-rao product (MTTKRP), and tensor times matrix-chain (TTMc) as described in Chapter 2. These dense tensor kernels have regular memory access patterns and high parallelism, making them a good match for spatial architectures. Yet how to productively accelerate the tensor kernels on spatial architectures for high performance remains a challenge. First, tensors often have many dimensions and a tensor kernel can involve many tensors. Second, every tensor kernel has many possible designs. Implementing any design efficiently on spatial hardware like FPGAs usually takes significant engineering effort.

In this chapter, I show that T2S-Tensor enables dense tensor kernels to be succinctly expressed and effectively optimized.

The major technical contributions of this chapter are as follows:

- I propose a concise yet expressive programming abstraction that decouples a spatial mapping from the functional specification of a dense tensor computation. The spatial mapping can direct the compiler to realize many sophisticated optimizations, achieving productivity and performance at the same time.

- I identify a set of key compiler optimizations that are essential for creating high-performance spatial hardware for dense tensor computations, and implement them in a comprehensive compilation framework. The compiler further provides composability of these optimizations, where various combinations of transformations can be applied and the compiler automatically generates the correct low-level code.

- I demonstrate the efficacy of T2S-Tensor approach on an Arria-10 FPGA as well as a research CGRA by generating OpenCL and assembly code, respectively for the two architectures. The GEMM implementations using T2S-Tensor achieve 88% and 92% of the performance achieved by codes that were manually written, highly optimized, and extensively tuned by

experts, with only around 3% of engineering time (two weeks vs. 18 months on the FPGA, and three days vs. three months on the CGRA, respectively). The T2S-Tensor GEMM implementation on the Arria-10 FPGA is also 76% faster than a (tuned) NDRange-style OpenCL implementation [Inta].

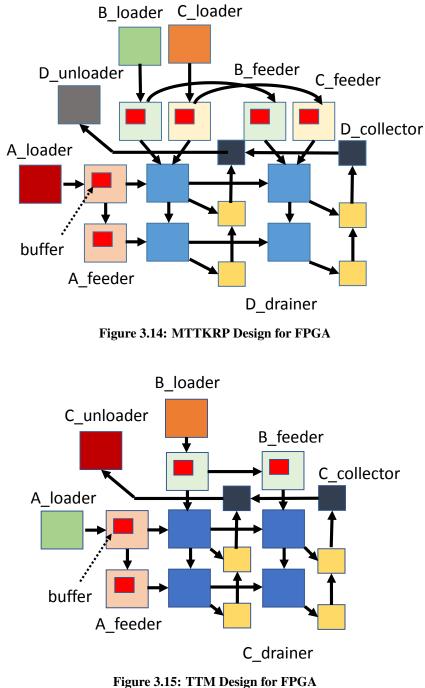

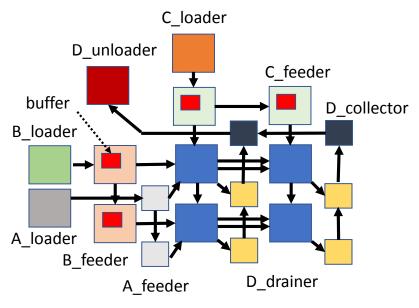

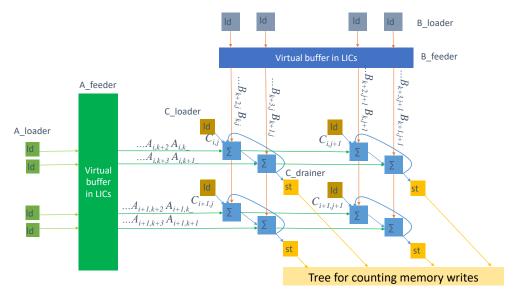

• Using this language, dense tensor factorization kernels, MTTKRP, TTM, and TTMc were also implemented in a productive and high-performance manner, and for the first time on spatial architectures.

The rest of the chapter is organized as follows: Section 3.2 gives a brief overview of the programming model; in Section 3.3 I illustrate the spatial optimizations in this system with GEMM as a working example; the compiler flow and optimizations are described in Section 3.4, followed by experimental results in Section 3.5, and related work in Section 3.6. Finally, Section 3.7 concludes this chapter.

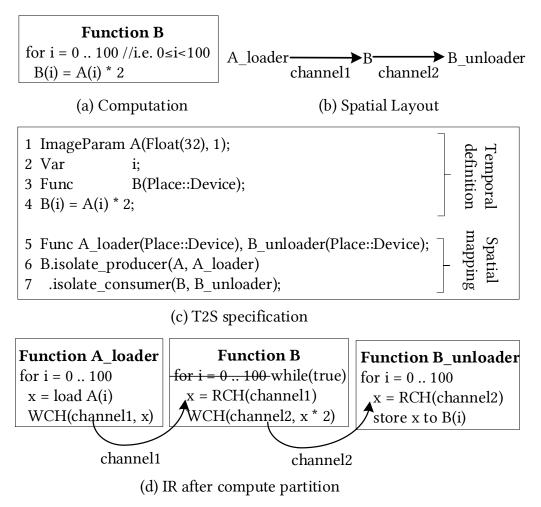

### **3.2 T2S-Tensor: Overview of the Programming Model**

A T2S-Tensor program is a specification embedded in C++. It consists of two parts: a temporal definition and a spatial mapping. The former defines a tensor computation functionally, while the latter specifies how to map the computation to a spatial architecture. In this chapter, I describe the programming abstraction with small intuitive examples to facilitate understanding. The same principle can be applied to construct very sophisticated spatial designs.

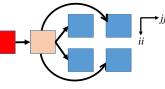

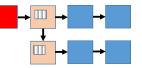

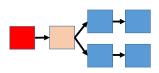

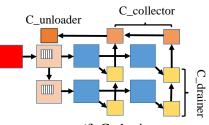

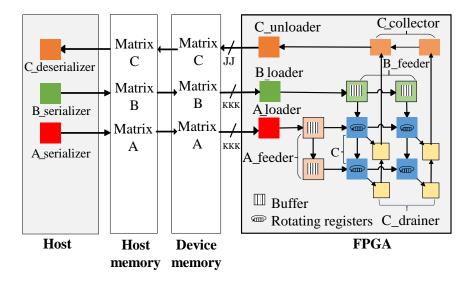

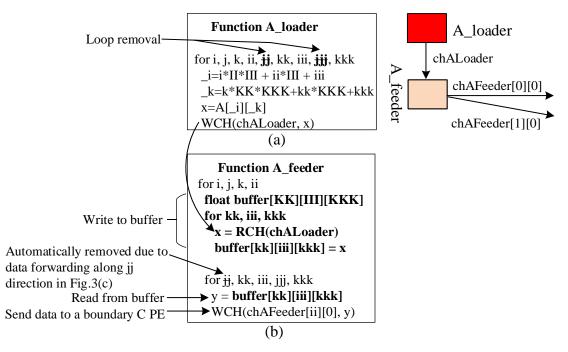

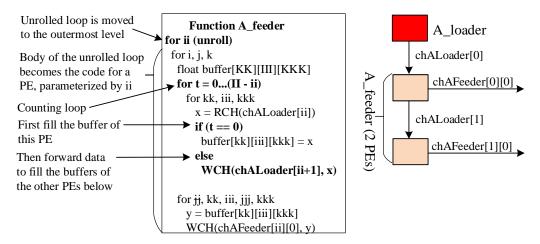

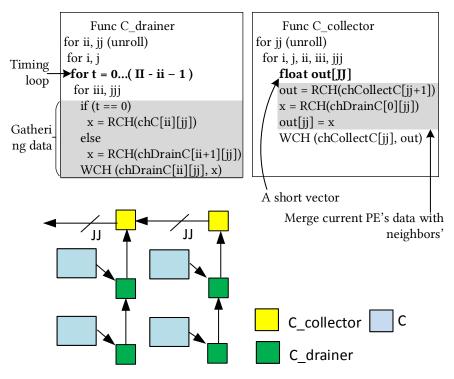

Fig. 3.1(a) shows a trivial computation that computes a function B with an input vector A. To map it to a spatial architecture, I isolate two functions: A\_loader for loading the input values and B\_unloader for saving the computed values from function B. This is called *compute partition*, which leads to a spatial layout shown in Fig. 3.1(b).

A corresponding T2S-Tensor specification is shown in Fig. 3.1(c). Lines 1-4 are the temporal definition expressing the original computation, where A is a one-dimensional single-precision floating-point vector, i is a variable, and B is a function that is to be run on the device. The upper loop bound of 100 is set upon execution, which is not shown.

Lines 5-7 are the spatial mapping. A\_loader and B\_unloader are the two new functions on the device, isolated out of function B as a producer of the input values in A and a consumer of the

computed values in B, respectively. A more detailed intermediate representation (IR) after compute partition is shown in Fig. 3.1(d), where RCH and WCH are primitives of reading and writing a channel. All the functions have exactly the same loop structure. However, function A\_loader does nothing but loads the values of A and sends them to a channel, channel1. Function B reads data from channel1, performs computation, and sends the results to channel2. Function B\_unloader reads data from channel2, and stores it into memory.

The compute partition maintains the semantics of the original computation. Its purpose is to partition a computation into sub-computations, which in turn become accessible to optimizations and can be specialized individually (Section 3.4). For example, in the middle box of Fig. 3.1(d), the compiler finds that the loop variable i is no longer used, and all the inputs are from channel1. Therefore, the compiler may automatically replace the loop with an infinite loop, while(true), and the loop automatically executes (or stops) if data are (not) available in channel1. This optimization is called *loop infinitization*.

Assuming a temporal definition, usually including simple math equations, is correctly specified by the programmer, the compiler checks the spatial directives to ensure that they do not violate the semantics of the temporal definition. This provides a correctness guarantee of the generated hardware, and composability of the directives.

T2S-Tensor is built on Halide [RKBA<sup>+</sup>13], a domain-specific language (DSL) for image processing on CPUs and GPUs. A key strength of Halide is to decouple a functional specification from optimizations. Many important loop-nest optimizations (e.g., loop reordering and tiling) can be easily specified in Halide. T2S-Tensor extends Halide to spatial architectures with the following optimizations:

- Spatial layout: compute partition.

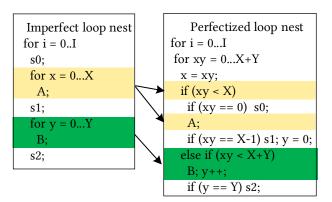

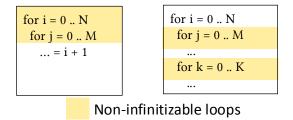

- *Loop transformations*: loop unrolling<sup>1</sup>, flattening, perfectization, infinitization, and removal.

- Data transformations: data forwarding, scattering, gathering, and vectorization.

- *Data caching*: single/double buffer insertion.

- *Control*: overlapping draining and filling of a pipeline, and drain signal generation.